科技發展日新月異,傳統的演算法在晶片下線後無法修改演算法行為,導致有些晶片雖然通過了 CP測試(Chip Probe Test,裸晶測試)和 FT 測試(Final Test,最終測試),但在使用過程中仍有可能出現缺陷的問題。若在此時新增測試演算法,將會增加不少的測試時間和成本。因此,演算法的彈性化與複雜度成為一門重要的課題。

芯測科技所開發的 TEC (Test Element Change) 以 GUI (圖形化操作介面)將演算法的行為元素化,藉由元素的重新排列,組合成新型態的演算法。即使客戶未採用芯測科技的 MBIST 電路,也可以保留原始的 BIST 架構,並以 EZ-TEC SRAM BIST IP 的形式插入原始電路,為客戶的整體應用帶來極大的便利性和彈性。當使用者發現 SRAM 有問題卻無法以原始 MBIST 電路偵測出 Defect,在不修改 SRAM 架構的前提下,使用者可以透過 EZ-TEC SRAM BIST IP 增加新的測試演算法來解決 Defect 問題,有效提高良率。

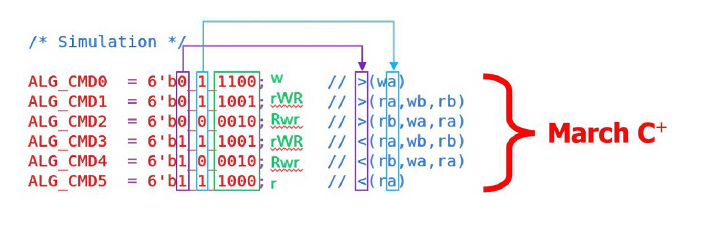

EZ-TEC SRAM BIST IP 是基於芯測科技美國專利「METHOD FOR GENERATING AN MEMORY BUILT-IN SELF-TEST ALGORITHM CIRCUIT」的元素化架構,每個元素都有相對應代碼,透過代碼即可產生新的演算法。使用者只需準備『四』個元素,就可以組合成常見的 March C+ 演算法,如下圖。

EZ-TEC SRAM BIST IP 主要優勢

⚫ 獨立運行於任何 MBIST並與現有的記憶體測試電路並存。

⚫ 原始 MBIST 電路無法檢測出特殊記憶體缺陷時,可透過元素重組重新測試。

⚫ 透過 Building-Block 架構能構建出最具成本效益的電路。

⚫ 針對重要的記憶體重組新的演算法來進行測試,確保記憶體測試的覆蓋率。

⚫ 輕鬆選擇記憶體測試演算法元素,提高晶片設計的靈活性和可靠性。

⚫ 有效降低 DPPM 與測試成本。

芯測科技的 EZ-TEC SRAM BIST IP 提供彈性重組測試演算法。能在 CP/FT 階段,讓測試工程師修改測試機台的 Pattern,進而提高記憶體測試的強度,為使用者帶來極大的便利性與彈性